The “monolithic AC-LGAD” is a newborn project aiming to design, produce, test and optimize a new generation of

After having demonstrated, through the ARCADIA experiment, that it is possible to produce working CMOS-LGAD detectors [1], the monolithic AC-LGAD projects wants to push state-of-the-art silicon detectors to unprecedented efficiency standards. Indeed, the CMOS integration ensures the optimal coupling between the sensor and its read-out chain, low material budget, low power consumption and, thanks to the standard process, low cost per unit area. At the same time, the AC-LGAD technology allows to achieve large and fast signals suitable for time of arrival measurements and, simultaneously, outstanding space resolutions. This is possible thanks to the charge sharing principle, achieved through the so-called RSD (Resistive AC-Coupled Silicon Detectors) paradigm [2].

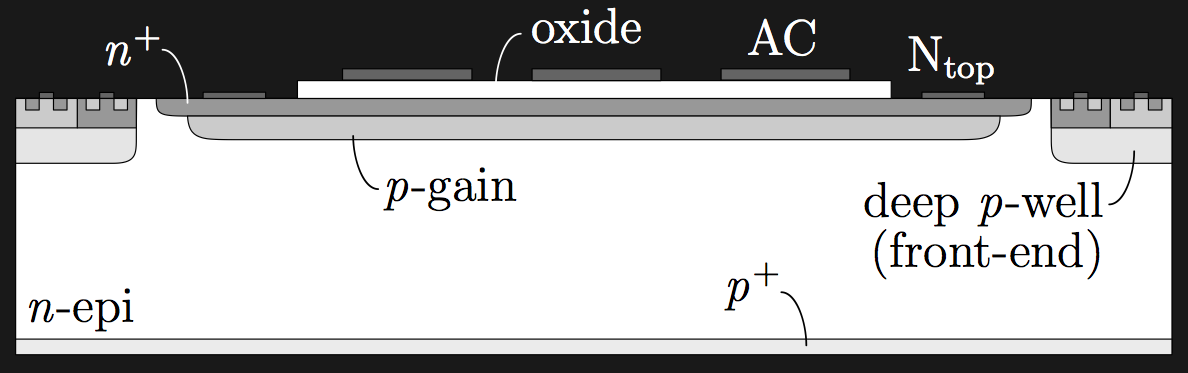

RSD is a technology that exploits a homogeneous and continuous resistive n-cathode and gain layer implants, in combination with a dielectric stack deposited on top of silicon, on which some metal pads are placed. The continuous active layer enables a 100% fill-factor detection, preserving the multimplication field continuity and, thus, improving the timing performances. At the same time, the dielectric layer works as a medium for the capacitive coupling between the resistive cathode and the metal pads. So, while the multiplied electrons discharge through the cathode, bipolar signals with amplitude proportional to the distance from the hit point are produced on the pads. This intrinsic analog signal formation is the key-element enabling the extraordinary precision in the spatial reconstruction of tracks.

The concept of monolithic AC-LGAD and the production process are covered by a pending patent. The project is actually under development and the first prototypes will be available as soon as the project is funded. Under the technology standpoint, the internal gain expected for these sensors is in the range from 10 to 30, which should allow to obtain micronlevel and sub-20-ps 4D resolutions. More details on the project will be provided in this webpage.

[1] T. Corradino et al., JINST 19(02), C02036 (2024), DOI: 10.1088/1748-0221/19/02/C02036

[2] M. Mandurrino et al., IEEE EDL 40(11), 1780-1783 (2019), DOI: 10.1109/LED.2019.2943242